September 1991

## LT1074/LT1076 Design Manual

Carl Nelson

#### INTRODUCTION

The use of switching regulators increased dramatically in the 1980's and this trend remains strong going into the 90s. The reasons for this are simple; heat and efficiency. Today's systems are shrinking continuously, while simultaneously offering greater electronic "horsepower." This combination would result in unacceptably high internal temperatures if low efficiency linear supplies were used. Heat sinks do not solve the problem in general because most systems are closed, with low thermal transfer from "inside" to "outside."

Battery powered systems need high efficiency supplies for long battery life. Topological considerations also require switching technology. For instance, a battery cannot generate an output higher than itself with linear supplies. The availability of low cost rechargeable batteries has created a spectacular rise in the number of battery powered systems, and consequently a matching rise in the use of switching regulators.

The LT1074 and LT1076 switching regulators are designed specifically for ease of use. They are close to the ultimate "three terminal box" concept which simply reguires an input, output and ground connection to deliver power to the load. Unfortunately, switching regulators are not horseshoes, and "close" still leaves room for egregious errors in the final execution. This Application Note is intended to eliminate the most common errors that customers make with switching regulators as well as offering some insight into the inner workings of switching designs. There is also an entirely new treatment of inductor design based on the mathematical models of core loss and peak current. This allows the customer to quickly see the allowable limits for inductor value and make an intelligent decision based on the need for cost, size, etc. The procedure differs greatly from previous design techniques and

many experienced designers at first think it can't work. They quickly become silent after standard laborious trial-and-error techniques yield identical results.

There is an old adage in woodworking — "Measure twice, cut once." This advice holds for switching regulators, also. Read AN44 through quickly to familiarize yourself with the contents. Then reread the pertinent sections carefully to avoid "cutting" the design two, three, or four times. Some switching regulator errors, such as excessive ripple current in capacitors, are time bombs best fixed *before* they are expensive field failures.

Since this paper was originally written, Linear Technology has produced a CAD program for switching regulators called SwitcherCAD. This program uses the ideas presented in this application note, but adds an extra level of accuracy by factoring in more second order effects. It also takes the drudgery out of the iterative design procedure. allowing rapid "what if" exploration. I highly recommend using SwitcherCAD after absorbing the basic concepts presented here. It cuts design time considerably, presents detailed information on operating conditions, and has many safeguards to prevent unreliable designs. One caution, however; SwitcherCAD has an initial run sequence, called Novice Mode, which generates a very conservative design from database components. The results of this initial design may not correlate with AN44 procedures because of assumptions used in SwitcherCAD and because of the limited number of components in the database. Changing to Expert Mode allows all components to be changed at will.

SwitcherCAD does not calculate components for loop stability. Linear Technology will be creating several separate programs for this purpose during 1993. Contact our Application department for details.

## TABLE OF CONTENTS

| INTRODUCTION                                                                                                                                                                                                          | AN44-1                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                              | AN44-3                                                         |

| PACKAGE/ORDER INFORMATION                                                                                                                                                                                             | AN44-3                                                         |

| ELECTRICAL CHARACTERISTICS                                                                                                                                                                                            | AN44-3                                                         |

| BLOCK DIAGRAM                                                                                                                                                                                                         | AN44-5                                                         |

| BLOCK DIAGRAM DESCRIPTION                                                                                                                                                                                             | AN44-6                                                         |

| TYPICAL PERFORMANCE CHARACTERISTICS                                                                                                                                                                                   | AN44-7                                                         |

| PIN DESCRIPTIONS  V <sub>IN</sub> Pin  Ground Pin  Feedback Pin  Shutdown Pin  Status Pin  I <sub>LIM</sub> Pin  Error Amplifier                                                                                      | AN44-10<br>AN44-10<br>AN44-11<br>AN44-13<br>AN44-14            |

| DEFINITION OF TERMS                                                                                                                                                                                                   | AN44-16                                                        |

| POSITIVE STEP-DOWN (BUCK) CONVERTER Inductor Output Catch Diode LT1074 Power Dissipation Input Capacitor (Buck Converter) Output Capacitor Efficiency Output Divider Output Overshoot Overshoot Fixes that Don't Work | AN44-19<br>AN44-20<br>AN44-20<br>AN44-21<br>AN44-22<br>AN44-22 |

| TAPPED-INDUCTOR BUCK CONVERTER<br>Snubber<br>Output Ripple Voltage<br>Input Capacitor                                                                                                                                 | AN44-25<br>AN44-26                                             |

| POSITIVE TO NEGATIVE CONVERTER Input Capacitor Output Capacitor Efficiency                                                                                                                                            | AN44-28<br>AN44-29                                             |

| NEGATIVE BOOST CONVERTER                              | . AN44-31 |

|-------------------------------------------------------|-----------|

| Output Diode                                          |           |

| Output Capacitor                                      |           |

| Output Ripple                                         |           |

| Input Capacitor                                       | . AN44-33 |

| INDUCTOR SELECTION                                    | . AN44-33 |

| Minimum Inductance to Achieve a Required              |           |

| Output Power                                          | . AN44-34 |

| Minimum Inductance Required to Achieve                |           |

| a Desired Core Loss                                   | . AN44-35 |

| MICROPOWER SHUTDOWN                                   | . AN44-38 |

| Start-Up Time Delay                                   | . AN44-38 |

| 5-PIN CURRENT LIMIT                                   | . AN44-39 |

| SOFT START                                            | . AN44-39 |

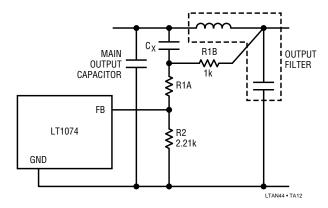

| OUTPUT FILTERS                                        | . AN44-40 |

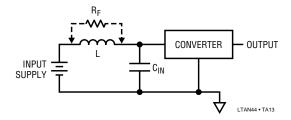

| INPUT FILTERS                                         | . AN44-42 |

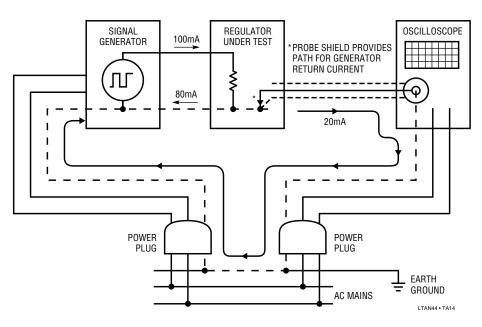

| OSCILLOSCOPE TECHNIQUES                               | . AN44-43 |

| Ground Loops                                          | . AN44-43 |

| Miscompensated Scope Probe                            |           |

| Ground "Clip" Pickup                                  |           |

| Wires Are Not Shorts                                  | . AN44-44 |

| EMI SUPPRESSION                                       | . AN44-45 |

| TROUBLESHOOTING HINTS                                 | . AN44-46 |

| Low Efficiency                                        | . AN44-46 |

| Alternating Switch Timing                             |           |

| Input Supply Won't Come Up                            |           |

| Switching Frequency Is Low In Current Limit           |           |

| IC Blows Up!                                          |           |

| IC Runs Hot                                           |           |

| High Output Ripple or Noise Spikes                    |           |

| Poor Load or Line Regulation                          | . AN44-47 |

| 500kHz-5MHz Oscillations, Especially at<br>Light Load | ANIAA 47  |

| LIGHT LOAD                                            | . AN44-4/ |

## **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage                                                                                                                                           |                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| LT1074/ LT1076                                                                                                                                          | 45V                                          |

| LT1074HV/76HV                                                                                                                                           |                                              |

| Switch Voltage with Respect to Input Voltage                                                                                                            |                                              |

| LT1074/ 76                                                                                                                                              | . 64V                                        |

| LT1074HV/76HV                                                                                                                                           | . 75V                                        |

| Switch Voltage with Respect to Ground Pin (V <sub>SW</sub> Nega                                                                                         | ative)                                       |

| LT1074/76 (Note 6)                                                                                                                                      | . 35V                                        |

| LT1074HV/76HV (Note 6)                                                                                                                                  | 45V                                          |

| Feedback Pin Voltage2V,                                                                                                                                 | +10V                                         |

| Shutdown Pin Voltage (Not to Exceed V <sub>IN</sub> )                                                                                                   | 40V                                          |

| Ctatua Din Valtaga                                                                                                                                      | 001/                                         |

| Status Pin Voltage                                                                                                                                      | . 300                                        |

| (Current Must Be Limited to 5mA When Status P                                                                                                           |                                              |

|                                                                                                                                                         |                                              |

| (Current Must Be Limited to 5mA When Status P                                                                                                           | in                                           |

| (Current Must Be Limited to 5mA When Status P<br>Switches "On")<br>I <sub>LIM</sub> Pin Voltage (Forced)<br>Maximum Operating Ambient Temperature Range | in<br>5.5V                                   |

| (Current Must Be Limited to 5mA When Status P<br>Switches "On")<br>I <sub>LIM</sub> Pin Voltage (Forced)                                                | in<br>5.5V                                   |

| (Current Must Be Limited to 5mA When Status P<br>Switches "On")<br>I <sub>LIM</sub> Pin Voltage (Forced)<br>Maximum Operating Ambient Temperature Range | in<br>5.5V<br>70°C                           |

| (Current Must Be Limited to 5mA When Status P<br>Switches "On")<br>I <sub>LIM</sub> Pin Voltage (Forced)                                                | in<br>5.5V<br>70°C                           |

| (Current Must Be Limited to 5mA When Status P Switches "On")  I <sub>LIM</sub> Pin Voltage (Forced)                                                     | 5.5V<br>70°C<br>25°C<br>25°C                 |

| (Current Must Be Limited to 5mA When Status P Switches "On")  I <sub>LIM</sub> Pin Voltage (Forced)                                                     | 5.5V<br>70°C<br>25°C<br>25°C<br>50°C         |

| (Current Must Be Limited to 5mA When Status P Switches "On")  I <sub>LIM</sub> Pin Voltage (Forced)                                                     | 5.5V<br>70°C<br>25°C<br>25°C<br>25°C<br>50°C |

| (Current Must Be Limited to 5mA When Status P Switches "On")  I <sub>LIM</sub> Pin Voltage (Forced)                                                     | 5.5V<br>70°C<br>25°C<br>25°C<br>25°C<br>50°C |

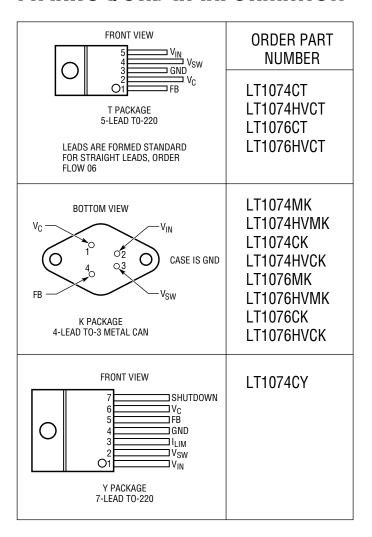

## PACKAGE/ORDER INFORMATION

# **ELECTRICAL CHARACTERISTICS** $T_j = 25^{\circ}C$ , $V_{IN} = 25V$ , unless otherwise noted.

| PARAMETER                    | CONDITIONS                                                                                                                                          |   | MIN | TYP             | MAX                       | UNITS          |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----------------|---------------------------|----------------|

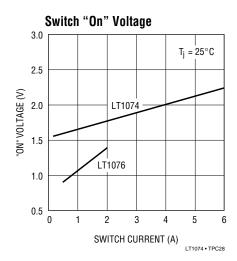

| Switch "On" Voltage (Note 1) | LT1074 $I_{SW} = 1A, T_j \ge 0^{\circ}C$<br>$I_{SW} = 1A, T_j < 0^{\circ}C$<br>$I_{SW} = 5A, T_j \ge 0^{\circ}C$<br>$I_{SW} = 5A, T_j < 0^{\circ}C$ |   |     |                 | 1.85<br>2.1<br>2.3<br>2.5 | V<br>V<br>V    |

|                              | LT1076 I <sub>SW</sub> = 0.5A<br>I <sub>SW</sub> = 2A                                                                                               | • |     |                 | 1.2<br>1.7                | V<br>V         |

| Switch "Off" Leakage         | LT1074 $V_{IN} \le 25V$ , $V_{SW} = 0$<br>$V_{IN} = V_{MAX}$ , $V_{SW} = 0$ (Note 7)                                                                |   |     | 5<br>10         | 300<br>500                | μΑ<br>μΑ       |

|                              | LT1076 $V_{IN} = 25V, V_{SW} = 0$<br>$V_{IN} = V_{MAX}, V_{SW} = 0 \text{ (Note 7)}$                                                                |   |     |                 | 150<br>250                | μA<br>μA       |

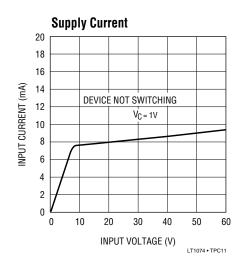

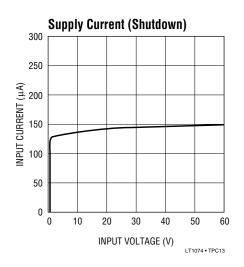

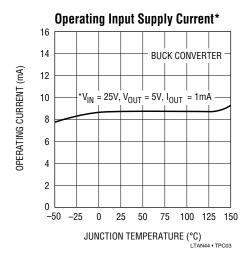

| Supply Current (Note 2)      | $V_{FB}$ = 2.5V, $V_{IN} \le 40V$<br>$40V < V_{IN} < 60V$<br>$V_{SHUT}$ = 0.1V (Device Shutdown) (Note 8)                                           | • |     | 8.5<br>9<br>140 | 11<br>12<br>300           | mA<br>mA<br>μA |

## **ELECTRICAL CHARACTERISTICS** $T_j = 25^{\circ}C$ , $V_{IN} = 25V$ , unless otherwise noted.

| PARAMETER                               | CONDITIONS                                                                                                               |                        | MIN        | TYP               | MAX               | UNITS                    |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------------------|-------------------|--------------------------|

| Minimum Supply Voltage                  | Normal Mode<br>Startup Mode (Note 3)                                                                                     |                        | 7.3<br>3.5 | 8<br>4.8          | V                 |                          |

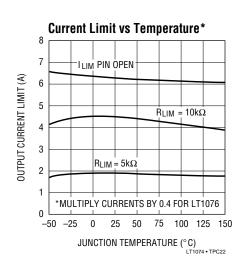

| Switch Current Limit (Note 4)           | LT1074 I <sub>LIM</sub> Open<br>R <sub>LIM</sub> = 10k (Note 5)<br>R <sub>LIM</sub> = 7k (Note 5)                        |                        | 5.5        | 6.5<br>4.5<br>3   | 8.5               | A<br>A<br>A              |

|                                         | LT1076 I <sub>LIM</sub> Open R <sub>LIM</sub> = 10k (Note 5) R <sub>LIM</sub> = 7k (Note 5)                              |                        | 2          | 2.6<br>1.8<br>1.2 | 3.2               | A<br>A<br>A              |

| Maximum Duty Cycle                      |                                                                                                                          | •                      | 85         | 90                |                   | %                        |

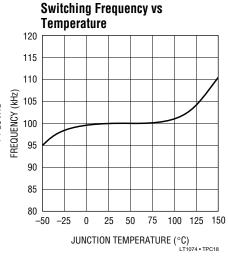

| Switching Frequency                     | $T_j \leq 125^{\circ}\text{C}$<br>$T_j > 125^{\circ}\text{C}$<br>$V_{FB} = 0\text{V through } 2k\Omega \text{ (Note 4)}$ | T <sub>j</sub> > 125°C |            | 100               | 110<br>120<br>125 | kHz<br>kHz<br>kHz<br>kHz |

| Switching Frequency Line Regulation     | $8V \le V_{IN} \le V_{MAX}$ (Note 7)                                                                                     | •                      |            | 0.03              | 0.1               | %/V                      |

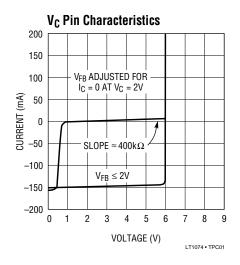

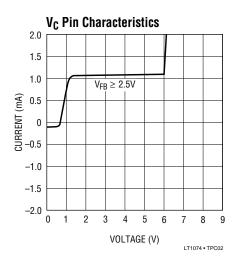

| Error Amplifier Voltage Gain (Note 6)   | $1V \le V_{\mathbb{C}} \le 4V$                                                                                           |                        |            | 2000              |                   | V/V                      |

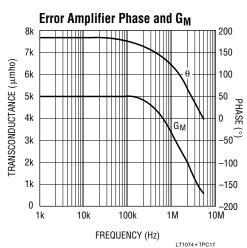

| Error Amplifier Transconductance        |                                                                                                                          |                        | 3700       | 5000              | 8000              | μmho                     |

| Error Amplifier Source and Sink Current | Source (V <sub>FB</sub> = 2V)<br>Sink (V <sub>FB</sub> = 2.5V)                                                           |                        | 100<br>0.7 | 140<br>1          | 225<br>1.6        | μA<br>mA                 |

| Feedback Pin Bias Current               | V <sub>FB</sub> = V <sub>REF</sub>                                                                                       | •                      |            | 0.5               | 2                 | μА                       |

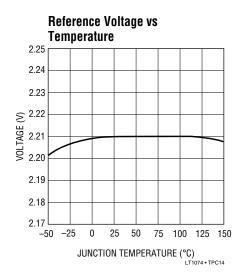

| Reference Voltage                       | V <sub>C</sub> = 2V                                                                                                      | •                      | 2.155      | 2.21              | 2.265             | V                        |

| Reference Voltage Tolerance             | V <sub>REF</sub> (Nominal) = 2.21V All Conditions of Input Voltage, Output Voltage, Temperature and Load Current         |                        |            | ± 0.5<br>± 1      | ± 1.5<br>± 2.5    | %<br>%                   |

| Reference Voltage Line Regulation       | $8V \le V_{IN} \le V_{MAX}$ (Note 7)                                                                                     | •                      |            | 0.005             | 0.02              | %/V                      |

| V <sub>C</sub> Voltage at 0% Duty Cycle |                                                                                                                          |                        |            | 1.5               |                   | V                        |

|                                         | Over Temperature                                                                                                         | •                      |            | - 4               |                   | mV/°C                    |

| Multiplier Reference Voltage            |                                                                                                                          |                        |            | 24                |                   | V                        |

| Shutdown Pin Current                    | $V_{SH} = 5V$ $V_{SH} \le V_{THRESHOLD} (\cong 2.5V)$ 5                                                                  |                        | 5          | 10                | 20<br>50          | μA<br>μA                 |

| Shutdown Thresholds                     | Switch Duty Cycle = 0 Fully Shut Down                                                                                    |                        | 2.2<br>0.1 | 2.45<br>0.3       | 2.7<br>0.5        | V                        |

| Status Window                           | As a Percent of Feedback Voltage                                                                                         |                        | 4          | ± 5               | 6                 | %                        |

| Status High Level                       | I <sub>STATUS</sub> = 10μA Sourcing                                                                                      |                        | 3.5        | 4.5               | 5.0               | V                        |

| Status Low Level                        | I <sub>STATUS</sub> = 1.6mA Sinking   ■                                                                                  |                        |            | 0.25              | 0.4               | V                        |

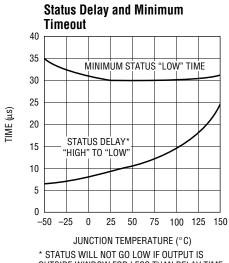

| Status Delay Time                       | 9                                                                                                                        |                        |            | μѕ                |                   |                          |

| Status Minimum Width                    |                                                                                                                          | 30                     |            |                   | μs                |                          |

| Thermal Resistance Junction to Case     |                                                                                                                          |                        | 2.5<br>4.0 | °C/W              |                   |                          |

The lacktriangle denotes the specifications which apply over the full operating temperature range.

**Note 1:** To calculate maximum switch "on" voltage at currents between low and high conditions, a linear interpolation may be used.

**Note 2:** A feedback pin voltage  $(V_{FB})$  of 2.5V forces the  $V_{C}$  pin to its low clamp level and the switch duty cycle to zero. This approximates the zero load condition where duty cycle approaches zero.

**Note 3:** Total voltage from  $V_{IN}$  pin to ground pin must be  $\geq$  8V after startup for proper regulation.

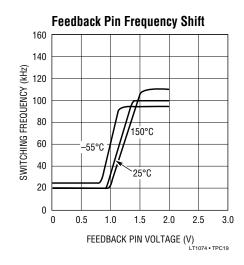

**Note 4:** Switch frequency is internally scaled down when the feedback pin voltage is less than 1.3V to avoid extremely short switch on times. During testing,  $V_{FB}$  is adjusted to give a minimum switch on time of  $1\mu s$ .

$$\label{eq:Note 5: I_LIM} \text{Note 5: } I_{LIM} \approx \frac{R_{LIM}-1k}{2k} \, (\text{LT1074}), \, I_{LIM} \approx \frac{R_{LIM}-1k}{5.5k} \, (\text{LT1076}).$$

**Note 6:** Switch to input voltage limitation must also be observed.

Note 7:  $V_{MAX} = 40V$  for the LT1074/76 and 60V for the LT1074HV/76HV.

Note 8: Does not include switch leakage.

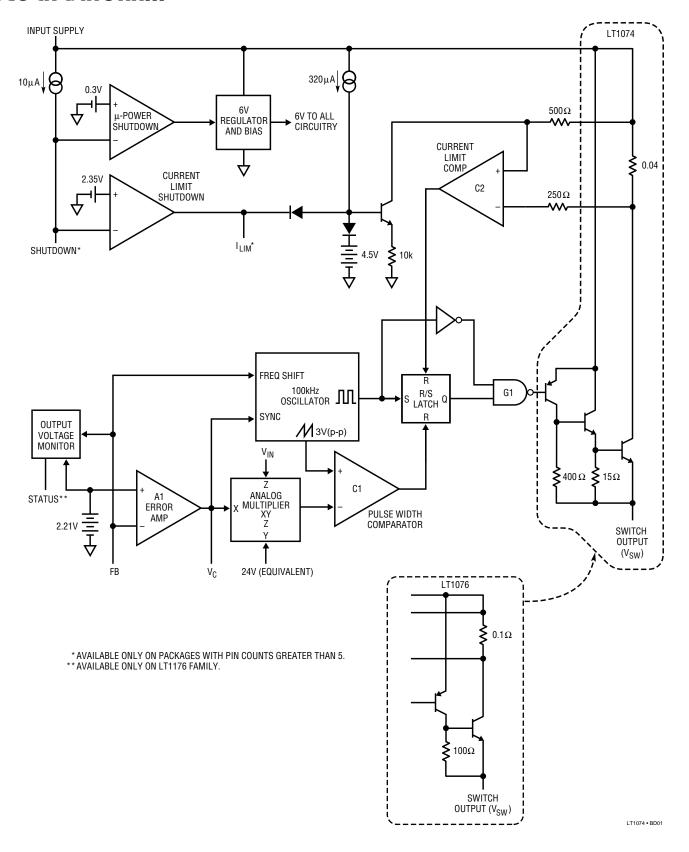

## **BLOCK DIAGRAM**

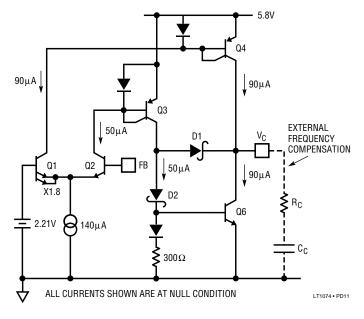

## BLOCK DIAGRAM DESCRIPTION

A switch cycle in the LT1074 is initiated by the oscillator setting the R/S latch. The pulse that sets the latch also locks out the switch via gate G1. The effective width of this pulse is approximately 700ns, which sets the maximum switch duty cycle to approximately 93% at 100kHz switching frequency. The switch is turned off by comparator C1, which resets the latch. C1 has a sawtooth waveform as one input and the output of an analog multiplier as the other input. The multiplier output is the product of an internal reference voltage, and the output of the error amplifier, A1, divided by the regulator input voltage. In standard buck regulators, this means that the output voltage of A1 required to keep a constant regulated output is independent of regulator input voltage. This greatly improves line transient response, and makes loop gain independent of input voltage. The error amplifier is a transconductance type with a  $G_M$  at null of approximately  $5000\mu$ mho. Slew current going positive is 140µA, while negative slew current is about 1.1mA. This asymmetry helps prevent overshoot on startup. Overall loop frequency compensation is accomplished with a series RC network from V<sub>C</sub> to ground.

Switch current is continuously monitored by C2, which resets the R/S latch to turn the switch off if an overcurrent condition occurs. The time required for detection and switch turn-off is approximately 600ns. So minimum switch "on" time in current limit is 600ns. Under dead shorted output conditions, switch duty cycle may have to be as low as 2% to maintain control of output current. This would require switch on time of 200ns at 100kHz switching frequency, so frequency is reduced at very low output

voltages by feeding the FB signal into the oscillator and creating a linear frequency downshift when the FB signal drops below 1.3V. Current trip level is set by the voltage on the  $I_{LIM}$  pin which is driven by an internal  $320\mu A$  current source. When this pin is left open, it self-clamps at about 4.5V and sets current limit at 6.5A for the LT1074 and 2.6A for the LT1076. In the 7-pin package an external resistor can be connected from the  $I_{LIM}$  pin to ground to set a lower current limit. A capacitor in parallel with this resistor will soft start the current limit. A slight offset in C2 guarantees that when the  $I_{LIM}$  pin is pulled to within 200mV of ground, C2 output will stay high and force switch duty cycle to zero.

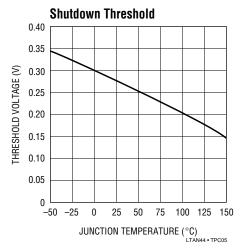

The "Shutdown" pin is used to force switch duty cycle to zero by pulling the  $I_{LIM}$  pin low, or to completely shut down the regulator. Threshold for the former is approximately 2.35V, and for complete shutdown, approximately 0.3V. Total supply current in shutdown is about 150 $\mu A$ . A 10 $\mu A$  pull-up current forces the shutdown pin high when left open. A capacitor can be used to generate delayed startup. A resistor divider will program "undervoltage lockout" if the divider voltage is set at 2.35V when the input is at the desired trip point.

The switch used in the LT1074 is a Darlington NPN (single NPN for LT1076) driven by a saturated PNP. Special patented circuitry is used to drive the PNP on and off very quickly even from the saturation state. This particular switch arrangement has no "isolation tubs" connected to the switch output, which can therefore swing to 40V below ground.

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

LTAN44 • TPC07

#### VIN PIN

The V<sub>IN</sub> pin is both the supply voltage for internal control circuitry and one end of the high current switch. It is important, *especially at low input voltages*, that this pin be bypassed with a low ESR, and low inductance capacitor to prevent transient steps or spikes from causing erratic operation. At full switch current of 5A, the switching transients at the regulator input can get very large as shown in Figure 1. Place the input capacitor very close to the regulator and connect it with wide traces to avoid extra inductance. Use radial lead capacitors.

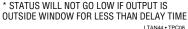

Figure 1. Input Capacitor Ripple

L<sub>P</sub> = Total inductance in input bypass connections and capacitor.

"Spike" height

$$\left(\frac{dI}{dt} \bullet L_P\right)$$

is approximately 2V *per inch* of lead length.

Step = 0.25V for ESR = 0.05 $\Omega$  and  $I_{SW}$  = 5A is 0.25V.

Step = 0.25V for ESR =  $0.05\Omega$  and  $I_{SW}$  = 5A is 0.25V. Ramp = 125mV for C = 200 $\mu$ F,  $T_{ON}$  = 5 $\mu$ s, and  $I_{SW}$  = 5A is 125mV.

Input current on the  $V_{IN}$  Pin in shutdown mode is the sum of actual supply current ( ${\approx}140\mu A,$  with a maximum of  $300\mu A)$  and switch leakage current. Consult factory for special testing if shutdown mode input current is critical.

#### **GROUND PIN**

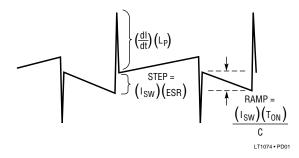

It might seem unusual to describe a ground pin, but in the case of regulators, the ground pin must be connected properly to ensure good load regulation. The internal reference voltage is referenced to the ground pin; so any error in ground pin voltage will be multiplied at the output;

$$\Delta V_{OUT} = \frac{\left(\Delta V_{GND}\right)\left(V_{OUT}\right)}{2.21}$$

To ensure good load regulation, the ground pin must be connected directly to the proper output node, so that no high currents flow in this path. The output divider resistor should also be connected to this low current connection line as shown in Figure 2.

Figure 2. Proper Ground Pin Connection

#### **FEEDBACK PIN**

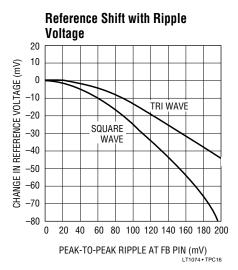

The feedback pin is the inverting input of an error amplifier which controls the regulator output by adjusting duty cycle. The non-inverting input is internally connected to a trimmed 2.21V reference. Input bias current is typically 0.5µA when the error amplifier is balanced ( $I_{OUT} = 0$ ). The error amplifier has asymmetrical  $G_M$  for large input signals to reduce startup overshoot. This makes the amplifier more sensitive to large ripple voltages at the feedback pin. 100mVp-p ripple at the feedback pin will create a 14mV offset in the amplifier, equivalent to a 0.7% output voltage shift. To avoid output errors, output ripple (p-p) should be less than 4% of DC output voltage at the point where the output divider is connected.

See the "Error Amplifier" section for more details.

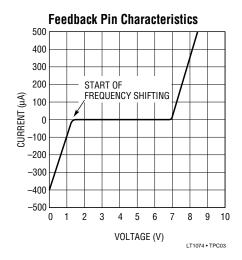

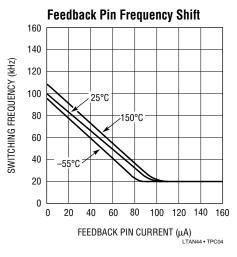

### Frequency Shifting at the Feedback Pin

The error amplifier feedback pin (FB) is used to downshift the oscillator frequency when the regulator output voltage is low. This is done to guarantee that output short circuit

current is well controlled even when switch duty cycle must be extremely low. Theoretical switch "on" time for a buck converter in continuous mode is:

$$t_{ON} = \frac{V_{OUT} + V_D}{V_{IN} \bullet f}$$

$V_D$  = Catch diode forward voltage (  $\approx 0.5V$ ) f = Switching frequency

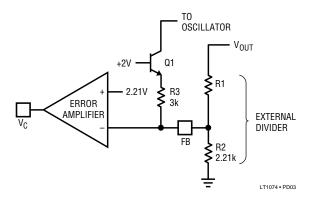

At f = 100kHz,  $t_{ON}$  must drop to 0.2 $\mu$ s when  $V_{IN}$  = 25V and the output is shorted ( $V_{OUT}$  = 0V). In current limit, the LT1074 can reduce  $t_{ON}$  to a minimum value of  $\approx$  0.6 $\mu$ s, much too long to control current correctly for  $V_{OUT}$  = 0. To correct this problem, switching frequency is lowered from 100kHz to 20kHz as the FB pin drops from 1.3V to 0.5V. This is accomplished by the circuitry shown in Figure 3.

Q1 is off when the output is regulating ( $V_{FB}=2.21V$ ). As the output is pulled down by an overload,  $V_{FB}$  will eventually reach 1.3V, turning on Q1. As the output continues to drop, Q1 current increases proportionately and lowers the frequency of the oscillator. Frequency shifting starts when the output is  $\approx 60\%$  of normal value, and is down to its minimum value of  $\cong 20$ kHz when the output is  $\cong 20\%$  of normal value. The rate at which frequency is shifted is determined by both the internal 3k resistor R3 and the external divider resistors. For this reason, R2 should not be increased to more than  $4k\Omega$ , if

the LT1074 will be subjected to the simultaneous conditions of high input voltage and output short circuit.

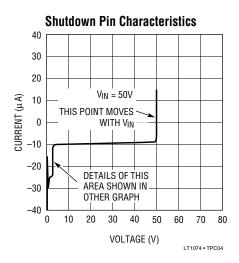

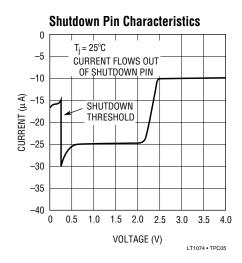

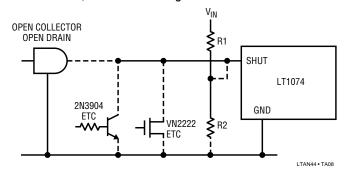

#### SHUTDOWN PIN

The shutdown pin is used for undervoltage lockout, micropower shutdown, soft start, delayed start, or as a general purpose on/off control of the regulator output. It controls switching action by pulling the  $I_{LIM}$  pin low, which forces the switch to a continuous "off" state. Full micropower shutdown is initiated when the shutdown pin drops below 0.3V.

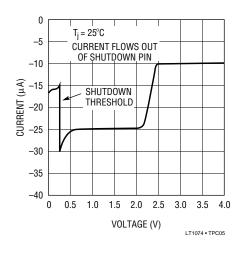

The V/I characteristics of the shutdown pin are shown in Figure 4. For voltages between 2.5V and  $\approx\!\!V_{IN}$ , a current of 10µA flows out of the shutdown pin. This current increases to  $\approx\!25\mu A$  as the shutdown pin moves through the 2.35V threshold. The current increases further to  $\approx\!30\mu A$  at the 0.3V threshold, then drops to  $\approx\!15\mu A$  as the shutdown voltage falls below 0.3V. The 10µA current source is included to pull the shutdown pin to its high or default state when left open. It also provides a convenient pullup for delayed start applications with a capacitor on the shutdown pin.

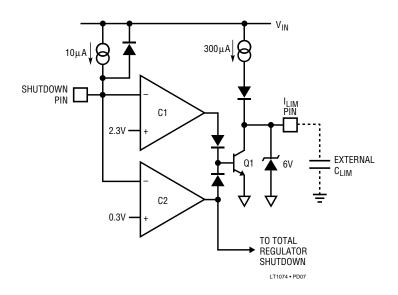

When activated, the typical collector current of Q1 in Figure 5, is  $\approx$  2mA. A soft start capacitor on the I<sub>LIM</sub> pin will delay regulator shutdown in response to C1, by  $\approx$ (5V)(C<sub>LIM</sub>)/2mA. Soft start after full micropower shutdown is ensured by coupling C2 to Q1.

Figure 3. Frequency Shifting

Figure 4. Shutdown Pin Characteristics

Figure 5. Shutdown Circuitry

## **Undervoltage Lockout**

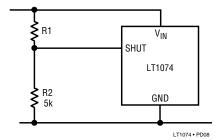

Undervoltage lockout point is set by R1 and R2 in Figure 6. To avoid errors due to the  $10\mu A$  shutdown pin current, R2 is usually set at 5k, and R1 is found from:

$$R1 = R2 \frac{\left(V_{TP} - V_{SH}\right)}{V_{SH}}$$

$V_{TP}$  = Desired undervoltage lockout voltage.

$V_{SH}$  = Threshold for lockout on the shutdown pin = 2.45V.

If quiescent supply current is critical, R2 may be increased up to 15k $\Omega$ , but the denominator in the formula for R2 should replace  $V_{SH}$  with  $V_{SH}$  – (10 $\mu$ A)(R2).

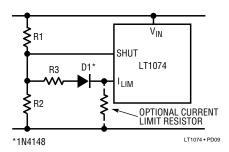

Hysteresis in undervoltage lockout may be accomplished by connecting a resistor (R3) from the  $I_{LIM}$  pin to the shutdown pin as shown in Figure 7. D1 prevents the shutdown divider from altering current limit.

Figure 6. Undervoltage Lockout

Figure 7. Adding Hysteresis

Trip Point =

$$V_{TP} = 2.35V \left(1 + \frac{R1}{R2}\right)$$

If R3 is added, the lower trip point ( $V_{IN}$  descending) will be the same. The upper trip point ( $V_{IITP}$ ) will be;

$$V_{UTP} = V_{SH} \left( 1 + \frac{R1}{R2} + \frac{R1}{R3} \right) - 0.8V \left( \frac{R1}{R3} \right)$$

If R1 and R2 are chosen, R3 is given by

$$R3 = \frac{\left(V_{SH} - 0.8V\right)\left(R1\right)}{V_{UTP} - V_{SH}\left(1 + \frac{R1}{R2}\right)}$$

**Example**: An undervoltage lockout is required such that the output will not start until  $V_{IN} = 20V$ , but will continue to operate until  $V_{IN}$  drops to 15V. Let R2 = 2.32k.

R1=

$$(2.32k)\frac{(15V-2.35V)}{2.35V}$$

=12.5k

R3= $\frac{(2.35-0.8)(12.5)}{20-2.35(1+\frac{12.5}{2.32})}$ =3.9k

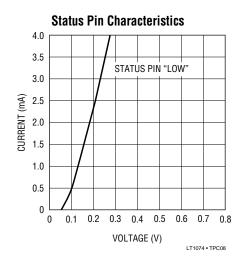

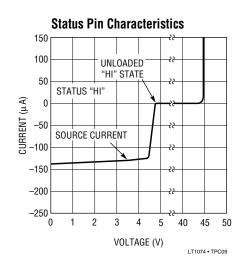

### STATUS PIN (AVAILABLE ONLY ON LT1176 PARTS)

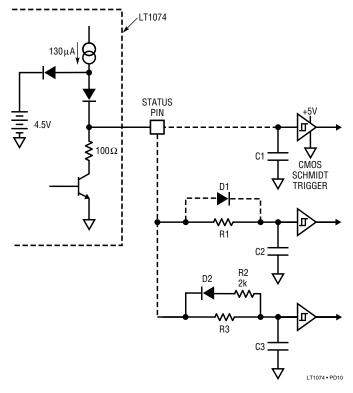

The status pin is the output of a voltage monitor "looking" at the feedback pin. It is low for a feedback voltage which is more than 5% above or below nominal. "Nominal" in this case means the internal reference voltage, so that the  $\pm 5\%$  window tracks the reference voltage. A time delay of  $\approx 10\mu s$  prevents short spikes from tripping the status low. Once it does go low, a second timer forces it to stay low for a minimum of  $\approx 30\mu s$ .

The status pin is modeled in Figure 8 with a  $130\mu A$  pullup to a 4.5V clamp level. The sinking drive is a saturated NPN with  $\approx \! 100\Omega$  resistance and a maximum sink current of approximately 5mA. An external pullup resistor can be added to increase output swing up to a maximum of 20V.

When the status pin is used to indicate "output OK," it becomes important to test for conditions which might create unwanted status states. These include output overshoot, large signal transient conditions, and excessive output ripple. "False" tripping of the status pin can usually be controlled by a pulse stretcher network as shown in Figure 8. A single capacitor (C1) will suffice to delay an output "OK" (status high) signal to avoid false "true" signals during start-up, etc. Delay time for status high will be approximately (2.3 x  $10^4$ ) (C1), or  $23\text{ms/}\mu\text{F}$ . Status low delay will be much shorter,  $\approx 600\mu\text{s/}\mu\text{F}$ .

Figure 8. Adding Time Delays to Status Output

If false tripping of status "low" could be a problem, R1 can be added. Delay of status high remains the same if R1  $\leq$  10k $\Omega$ . Status low delay is extended by R1 to approximately R1 • C2 seconds. Select C2 for high delay and R1 for low delay.

**Example**: Delay status high for 10ms, and status low for 3ms.

C2 =

$$\frac{10ms}{23ms/\mu F}$$

= 0.47 $\mu F$  (Use 0.47 $\mu F$ )

R1 =  $\frac{3ms}{C2}$  =  $\frac{3ms}{0.47\mu F}$  = 6.4 $k\Omega$

In this example D1 is not needed because R1 is small enough to not limit the charging of C2.

If very fast "low" tripping combined with long "high" delays is desired, use the D2, R2, R3, C3 configuration. C3 is chosen first to set "low" delay

$$C3 \approx \frac{t_{LOW}}{2k\Omega}$$

R3 is then selected for "high" delay

$$R3 \approx \frac{t_{HIGH}}{C3}$$

For  $t_{LOW}$  = 100 $\mu$ s and  $t_{HIGH}$  = 10ms, C3 = 0.05 $\mu$ F and R3 = 200k $\Omega$ .

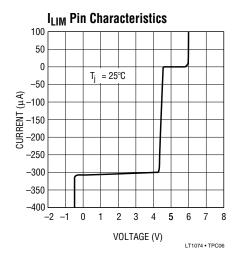

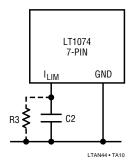

### I<sub>LIM</sub> PIN

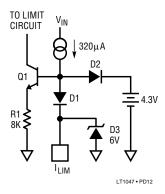

The I<sub>LIM</sub> pin is used to reduce current limit below the preset value of 6.5A. The equivalent circuit for this pin is shown in Figure 9.

When  $I_{LIM}$  is left open, the voltage at Q1 base clamps at 5V through D2. Internal current limit is determined by the current through Q1. If an external resistor is connected between  $I_{LIM}$  and ground, the voltage at Q1 base can be reduced for lower current limit. The resistor will have a voltage across it equal to (320 $\mu$ A) (R), limited to  $\approx$  5V when clamped by D2. Resistance required for a given current limit is

$$R_{LIM} = I_{LIM} (2k\Omega) + 1k\Omega (LT1074)$$

$$R_{LIM} = I_{LIM} (5.5k\Omega) + 1k\Omega (LT1076)$$

As an example, a 3A current limit would require 3A (2k) +  $1k = 7k\Omega$  for the LT1074. The accuracy of these formulas is  $\pm 25\%$  for  $2A \le I_{LIM} \le 5A$  (LT1074) and  $0.7A \le I_{LIM} \le 1.8A$  (LT1076), so  $I_{LIM}$  should be set at least 25% above the *peak* switch current required.

Figure 9. I<sub>LIM</sub> Pin Circuit

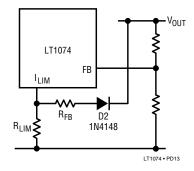

Foldback current limiting can be easily implemented by adding a resistor from the output to the  $I_{LIM}$  pin as shown in Figure 10. This allows full desired current limit (with or without  $R_{LIM}$ ) when the output is regulating, but reduces current limit under short circuit conditions. A typical value for  $R_{FB}$  is  $5k\Omega,$  but this may be adjusted up or down to set the amount of foldback. D2 prevents the output voltage from forcing current back into the  $I_{LIM}$  pin. To calculate a

Figure 10. Foldback Current Limit

value for R<sub>FB</sub>, first calculate R<sub>LIM</sub>, then R<sub>FB</sub>:

$$R_{FB} = \frac{\left(I_{SC} - 0.44^{*}\right)\left(R_{L}\right)}{0.5^{*}\left(R_{L} - 1k\Omega\right) - I_{SC}} = R_{L} \text{ ink}\Omega$$

\*Change 0.44 to 0.16, and 0.5 to 0.18 for LT1076.

**Example:**  $I_{LIM} = 4A$ ,  $I_{SC} = 1.5A$ ,  $R_{LIM} = (4)(2k) + 1k = 9k$

$$R_{FB} = \frac{(1.5 - 0.44)(9k\Omega)}{0.5(9k - 1k) - 1.5} = 3.8k\Omega$$

#### **ERROR AMPLIFIER**

The error amplifier in Figure 11 is a single stage design with added inverters to allow the output to swing above and below the common mode input voltage. One side of the amplifier is tied to a trimmed internal reference voltage of 2.21V. The other input is brought out as the FB (feedback) pin. This amplifier has a  $G_M$  (voltage "in" to current "out") transfer function of  ${\approx}5000\mu\text{mho}$ . Voltage gain is determined by multiplying  $G_M$  times the total equivalent output loading, consisting of the output resistance of Q4 and Q6 in parallel with the series RC external frequency compensation network. At DC, the external RC is ignored, and with a parallel output impedance for Q4 and Q6 of  $400\text{k}\Omega$ , voltage gain is  $\approx 2000$ . At frequencies above a few hertz, voltage gain is determined by the external compensation,  $R_C$  and  $C_C$ .

$$A_V = \frac{G_m}{2\pi \bullet f \bullet C_C}$$

at midfrequencies

$A_V = G_m \bullet R_C$  at high frequencies

Phase shift from the FB pin to the  $V_C$  pin is  $90^\circ$  at midfrequencies where the external  $C_C$  is controlling gain, then drops back to  $0^\circ$  (actually  $180^\circ$  since FB is an inverting input) when the reactance of  $C_C$  is small compared to  $R_C$ . The low frequency "pole" where the reactance of  $C_C$  is equal to the output impedance of Q4 and Q6  $(r_0)$ , is

$$f_{POLE} = \frac{1}{2\pi \cdot r_0 \cdot C} r_0 \approx 400 k\Omega$$

Although  $f_{POLE}$  varies as much as 3:1 due to  $r_{O}$  variations, mid-frequency gain is dependent only on  $G_{M}$ , which is specified much tighter on the data sheet. The higher frequency "zero" is determined solely by  $R_{G}$  and  $C_{G}$ .

$$f_{ZERO} = \frac{1}{2\pi \cdot R_C \cdot C_C}$$

The error amplifier has asymmetrical peak output current. Q3 and Q4 current mirrors are unity gain, but the Q6 mirror has a gain of 1.8 at output null and a gain of 8 when the FB pin is high (Q1 current = 0). This results in a maximum positive output current of  $140\mu A$  and a maximum negative (sink) output current of  $\cong 1.1 mA$ . The asymmetry is deliberate — it results in much less regulator output overshoot during rapid startup or following the release of an output overload. Amplifier offset is kept low by area scaling Q1 and Q2 at 1.8:1.

Amplifier swing is limited by the internal 5.8V supply for positive outputs and by D1 and D2 when the output goes low. Low clamp voltage is approximately one diode drop ( $\approx 0.7V - 2mV/^{\circ}C$ ).

Note that both the FB pin and the  $V_{\text{C}}$  pin have other internal connections. Refer to the frequency shifting and sychronizing discussions.

Figure 11. Error Amplifier

## **Application Note 44**

#### **DEFINITION OF TERMS**

V<sub>IN</sub>: DC input voltage.

$V_{IN}$ ': DC input voltage minus switch voltage loss.  $V_{IN}$ ' is 1.5 V to 2.3V less than  $V_{IN}$ , depending on switch current.

**V<sub>OUT</sub>:** DC output voltage.

$V_{OUT}$ ': DC output voltage plus catch diode forward voltage.  $V_{OUT}$ ' is typically 0.4V to 0.6V more than  $V_{OUT}$ .

**f:** Switching frequency.

$I_M$ : Maximum specified switch current  $I_M = 5.5A$  for the LT1074 and 2A for the LT1076.

**Isw:** Switch current during switch on time. The current typically jumps to a starting value, then ramps higher. Isw is the *average* value during this period unless otherwise stated. It is *not* averaged over the whole switching period, which includes switch off time.

**I<sub>OUT</sub>:** DC output current.

ILIM: DC output current limit.

**IDP:** Catch diode forward current. This is the peak current for discontinuous operation and the average value of the current *pulse* during switch off time for continuous mode.

**IDA:** Catch diode forward current averaged over one complete switching cycle. **IDA** is used to calculate diode heating.

$\Delta$ I: Peak-to-peak ripple current in the inductor, also equal to peak current in the discontinuous mode.  $\Delta$ I is used to calculate output ripple voltage and inductor core losses.

**Vp-p:** Peak-to-peak output voltage ripple. This does not include "spikes" created by fast rising currents and capacitor parasitic inductance.

$t_{SW}$ : This is not really an actual rise or fall time. Instead, it represents the *effective* overlap time of voltage and current in the switch.  $t_{SW}$  is used to calculate switch power dissipation.

**L:** Inductance, usually measured with low AC flux density, and zero DC current. Note that large AC flux density can increase L by up to 30%, and large DC currents can decrease L dramatically (core saturation).

**B**<sub>AC</sub>: *Peak* AC flux density in the inductor core, equal to one-half peak-to-peak AC flux density. Peak value is used because nearly all core loss curves are plotted with peak flux density.

**N:** Tapped-inductor or transformer turns ratio. Note the exact definition of N for each application.

$\mu$ : Effective permeability of core material used in the inductor.  $\mu$  is typically 25-150. Ferrite material is much higher, but is usually gapped to reduce the effective value to this range.

$V_e$ : Effective core material volume (cm<sup>3</sup>).

Le: Effective core magnetic path length (cm).

**A<sub>e</sub>:** Effective core cross sectional area (cm<sup>2</sup>).

Aw: Effective core or bobbin winding area.

Lt: Average length of one turn on winding.

$\mathbf{P_{CU}}$ : Power dissipation caused by winding resistance. It does not include skin effect.

**P<sub>C</sub>:** Power loss in the magnetic core. P<sub>C</sub> depends only on *ripple current* in the inductor not DC current.

**E**: Overall regulator efficiency. It is simply output power divided by input power.

#### **POSITIVE STEP-DOWN (BUCK) CONVERTER**

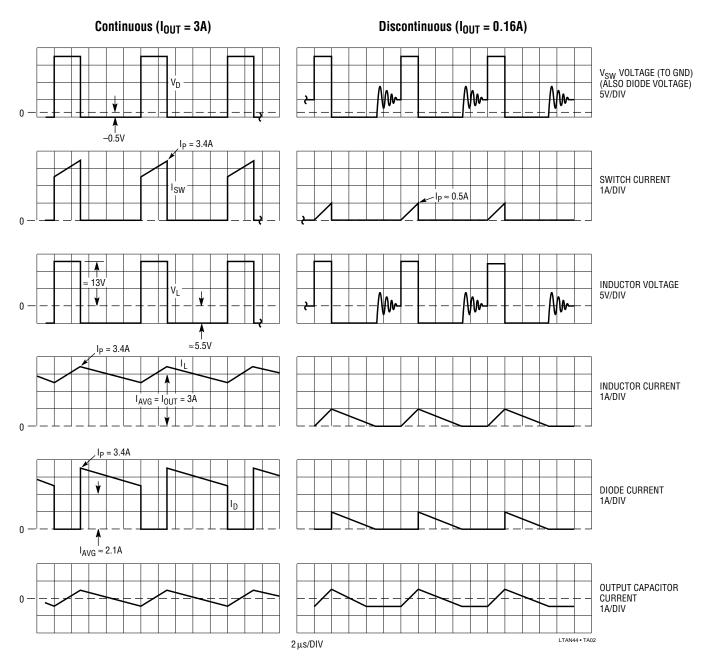

The circuit in Figure 12 is used to convert a larger positive input voltage to a lower positive output. Typical waveforms are shown in Figure 13, with  $V_{IN} = 20V$ ,  $V_{OUT} = 5V$ ,  $L = 50\mu H$ , for both continuous mode (inductor current never drops to zero) with  $I_{OUT} = 3A$  and discontinuous mode, where inductor current drops to zero during a portion of the switching cycle ( $I_{OUT} = 0.17A$ ). Continuous mode maximizes output power but requires larger inductors. *Maximum* output current in true discontinuous mode is only one-half of switch current rating. Note that when load current is reduced in a continuous mode design, eventually the circuit will enter discontinuous mode. The LT1074 operates equally well in either mode and there is no significant change in performance when load current reduction causes a shift to discontinuous mode.

Figure 12. Basic Positive Buck Converter

Duty cycle of a buck converter in continuous mode is

$$DC = \frac{V_{OUT} + V_f}{V_{IN} - V_{SW}} = \frac{V_{OUT}}{V_{IN}}$$

(01)

$V_f$  = Forward voltage of catch diode  $V_{SW}$  = Voltage loss across "on" switch

Note that duty cycle does not vary with load current except to the extent that  $V_f$  and  $V_{SW}$  change slightly.

A buck converter will change from continuous to discontinuous mode (and duty cycle will begin to drop) at a load current equal to

$$I_{OUT(CRIT)} = \frac{\left(V_{OUT}'\right)\left(V_{IN}' - V_{OUT}'\right)}{2 \bullet V_{IN}' \bullet f \bullet L}$$

(02)

With the possible exception of load transient response, there is no reason to increase L to ensure continuous mode operation at light load.

Using the values from Figure 12, with  $V_{IN}$  = 25V,  $V_f$  = 0.5V,  $V_{SW}$  = 2V

$$DC = \frac{5 + 0.5}{25 - 2} = 24\% \tag{03}$$

$$I_{OUT(CRIT)} = \frac{(5.5)(23 - 5.5)}{2(23)(10^5)(50 \times 10^{-6})} = 0.42A$$

The "ringing" which occurs at some point in the switch "off" cycle in discontinuous mode is simply the resonance created by the catch diode capacitance plus switch capacitance in parallel with the inductor. This ringing does no harm and any attempt to dampen it simply wastes efficiency. Ringing frequency is given by;

$$f_{RING} = \frac{1}{2\pi \sqrt{L \bullet \left(C_{SW} + C_{DIODE}\right)}}$$

(04)

$$C_{SW} \approx 80 pF$$

$C_{DIODF} = 200 pF - 1000 pF$

No off state ringing occurs in continuous mode because the diode is always conducting during switch off time and effectively shorts the resonance.

A detailed look at the leading edge of the switch waveform may reveal a second "ringing" tendency, usually at frequencies around 20MHz-50MHz. This is the result of the inductance in the loop which includes the input capacitor, the LT1074 leads, and the diode leads, combined with the capacitance of the catch diode. A total lead length of 4 inches will create  $\approx 0.1 \mu H$ . This coupled with 500pF of diode capacitance will create a damped 25MHz oscillation superimposed on the fast rising switch voltage waveform. Again, no harm is created by this ringing and no attempt should be made to dampen it other than minimizing lead length. Certain board layouts combined with very short interconnects and high diode capacitance may create a tuned circuit which resonates with the switch output to

Figure 13. Buck Converter Waveforms with  $V_{IN}$  = 20V, L =  $50\mu H$

cause a low amplitude oscillation at the switch output during "on" time. This can be eliminated with a ferrite bead slipped over either diode lead during board assembly.

It is interesting to note that standard silicon fast recovery diodes create almost no ringing because of their lower capacitance and because they are effectively damped by their slower turn-off characteristics. This slower turn-off and the larger forward voltage represent additional power loss, so Schottky diodes are normally recommended.

*Maximum* output current of a buck converter is given by;

Continuous Mode (05)

$$I_{OUT(MAX)} = I_{M} - \frac{V_{OUT}(V_{IN} - V_{OUT})}{2f \cdot V_{IN} \cdot L}$$

$I_{M}$  = Maximum switch current (5.5A for LT1074)

V<sub>IN</sub> = DC input voltage (maximum)

$V_{OUT} = Output \ voltage$

f = Switching frequency

For the example shown, with  $L = 50\mu H$ , and  $V_{IN} = 25V$ ,

$$I_{OUT(MAX)} = 5.5 - \frac{5(25-5)}{2(10^5)(25)(50 \times 10^{-6})} = 5.1A$$

(06)

Note that increasing inductor size to  $100\mu H$  would only increase maximum output current by 4%, but decreasing it to  $20\mu H$  would drop maximum current to 4.5A. Low inductance can be used for lower output currents, but core loss will increase.

#### Inductor

The inductor used in a buck converter acts as both an energy storage element and a smoothing filter. There is a basic tradeoff between good filtering versus size and cost. Typical inductor values used with the LT1074 range from  $5\mu H$  to  $200\mu H$ , with the small values used for lower power, minimum size applications and the larger values used to maximize output power or minimize output ripple voltage. The inductor must be rated for currents at least equal to output current and there are restrictions on ripple current (expressed as volt • microsecond product at various frequencies) to avoid core heating. For details on selecting an inductor and calculating losses, see the "Inductor Selection" section.

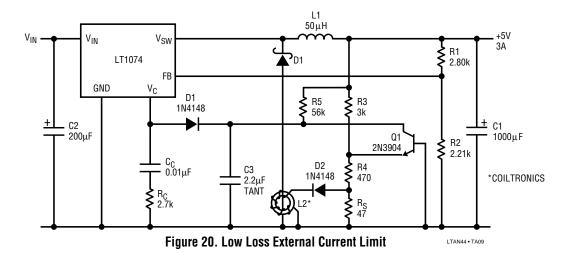

#### **Output Catch Diode**

D1 is used to generate a current path for L1 current when the LT1074 switch turns off. The current through D1 in continuous mode is equal to output current with a duty cycle of  $(V_{IN} - V_{OUT})/V_{IN}$ . For low input voltages, D1 may operate at duty cycles of 50% or less, but one must be very careful of utilizing this fact to minimize diode heat sinking. First, an unexpected high input voltage will cause duty cycle to increase. More important however, is a shorted output condition. When  $V_{OLIT} = 0$ , diode duty cycle is  $\approx 1$  for any input voltage. Also, in current limit, diode current is not load current, but is determined by LT1074 switch current limit. If continuous output shorts must be tolerated, D1 must be adequately rated and heat sunk. 7 and 11pin versions of the LT1074 allow current limit to be reduced to limit diode dissipation. 5-pin versions can be accurately current limited using the technique shown in Figure 20.

Under normal conditions, D1 dissipation is given by;

$$P_{DI} = I_{OUT} \frac{\left(V_{IN} - V_{OUT}\right)}{V_{IN}} \bullet V_{f}$$

(07)

$V_f$  is the forward voltage of D1 at  $I_{OUT}$  current. Schottky diode forward voltage is typically 0.6V at the diode's full rated current, so it is normal design practice to use a diode rated at 1.5 to 2 times output current to maintain efficiency and allow margin for short circuit conditions. This derating allows  $V_f$  to drop to approximately 0.5V

**Example:**  $V_{IN(MAX)} = 25V$ ,  $I_{OUT} = 3A$ ,  $V_{OUT} = 5V$ , assume  $V_f = 0.5V$ ;

Full Load (08)

$$P_{DI} = \frac{(3)(25-5)(0.5V)}{25} = 1.2W$$

Shorted Output

$$P_{DI} = (\approx 6A) (DC = 1) (0.6V) = 3.6W$$

The high diode dissipation under shorted output conditions may necessitate current limit adjustment if adequate heat sinking cannot be provided.

Diode switching losses have been neglected because the reverse recovery time is assumed to be short enough to ignore. If a standard silicon diode is used, switching losses cannot be ignored. They can be approximated by:

$$Pt_{rr} \approx (V_{IN})(f)(t_{rr})(I_{OUT})$$

(09)

$t_{rr}$  = Diode reverse recovery time

**Example:** Same circuit with  $t_{rr} = 100$ ns

$$Pt_{rr} = (25)(10^5)(10^{-7})(3) = 0.75W$$

(10)

Diodes with abrupt turn-off characteristics will transfer most of this power to the LT1074 switch. Soft recovery diodes will dissipate much of the power within the diode itself.

#### LT1074 Power Dissipation

The LT1074 draws about 7.5mA quiescent current, independent of input voltage or load. It draws an additional 5mA during switch "on" time. The switch itself dissipates a power approximately proportional to load current. This power is due to pure conduction losses (switch "on" voltage times switch current) and dynamic switching losses due to finite switch current rise and fall times. Total LT1074 power dissipation can by calculated from

$$P = V_{IN} \left[ 7mA + 5mA \bullet DC + 2I_{OUT} \bullet t_{SW} \bullet f \right] + (11)$$

$$DC \left[ I_{OUT} \left( 1.8V \right)^* + 0.1\Omega^* \left( I_{OUT} \right)^2 \right]$$

$$DC = Duty \ Cycle \approx \frac{V_{OUT} + 0.5V}{V_{IN} - 2V}$$

t<sub>SW</sub> = Effective overlap time of switch voltage and current

$$\approx 50 \text{ns} + (3 \text{ns/A}) (I_{OUT}) \quad (LT1074)$$

$\approx 60 \text{ns} + (10 \text{ns/A}) (I_{OUT}) \quad (LT1076)$

**Example:**  $V_{IN} = 25V$ ,  $V_{OUT} = 5V$ , f = 100kHz,  $I_{OUT} = 3A$

$$DC = \frac{5 + 0.5}{25 - 2} = 0.196 \tag{12}$$

$$t_{SW} = 50 \text{ns} + (3 \text{ns/A})(3 \text{A}) = 59 \text{ns}$$

$$P = (13)$$

$$25 \left[ \frac{7\text{mA} + 5\text{mA} (0.196) + (2) (3) (59\text{ms}) (10^5)}{(2) (3) (59\text{ms}) (10^5)} \right] + 0.196 \left[ 3 (1.8) + 0.1 (3)^2 \right]$$

$$= \underbrace{0.21\text{W} + 0.89\text{W} + 1.24\text{W}}_{\text{Supply}} = 2.34\text{W}$$

Supply Dynamic Switch Switch Current Switching Conduction

Loss

\*LT1076 = 1V,  $0.3\Omega$

Loss

#### **Input Capacitor (Buck Converter)**

Loss

A local input bypass capacitor is normally required for buck converters because the input current is a square wave with fast rise and fall times. This capacitor is chosen by ripple current rating—the capacitor must be large enough to avoid overheating created by its ESR and the AC

RMS value of converter input current. For continuous mode;

$$I_{AC,RMS} = I_{OUT} \sqrt{\frac{V_{OUT} \left(V_{IN} - V_{OUT}\right)}{\left(V_{IN}\right)^2}}$$

(14)

Worst case is at  $V_{IN} = 2V_{OUT}$ .

Power loss in the input capacitor is not insignificant in high efficiency applications. It is simply RMS capacitor current squared times ESR.

$$P_{C3} = \left(I_{AC, RMS}\right)^2 (ESR) \tag{15}$$

**Example:**  $V_{IN} = 20V-30V$ ,  $I_{OUT} = 3A$ ,  $V_{OUT} = 5V$ .

Worst case is at  $V_{IN} = 2 \cdot V_{OUT} = 10V$ , so use the closest  $V_{IN}$  value of 20V:

$$I_{AC, RMS} = 3A \sqrt{\frac{5(20-5)}{(20)^2}} = 1.3A RMS$$

(16)

The input capacitor must be rated at a working voltage of 30V minimum and 1.3A ripple current. Ripple current ratings vary with maximum ambient temperature, so check data sheets carefully.

It is important to locate the input capacitor very close to the LT1074 and to use short leads (radial) when the DC input voltage is less than 12V. Spikes as high as 2V/inch of lead length will appear at the regulator input. If these spikes drop below  $\approx\!7\text{V}$ , the regulator will exhibit anomalous behavior. See "V\_IN Pin" in the Pin Descriptions section.

You may be wondering why no mention has been made of capacitor value. That's because it doesn't really matter. Larger electrolytic capacitors are purely resistive (or inductive) at frequencies above 10kHz, so their bypassing impedance is resistive, and ESR is the controlling factor. For input capacitors used with the LT1074, a unit which meets ripple current ratings will provide adequate "bypassing" regardless of its capacitance value. Units with higher voltage rating will have lower capacitance for the same ripple current rating, but as a general rule, the volume required to meet a given ripple current/ESR is fixed over a wide range of capacitance/voltage rating. If the capacitor chosen for this application has  $0.1\Omega$  ESR, it will have a power loss of  $(1.3A)^2$   $(0.1\Omega) = 0.17W$ .

### **Output Capacitor**

In a buck converter, output ripple voltage is determined by both the inductor value and the output capacitor;

Continuous Mode (17)

$$Vp - p = \frac{\left(ESR\right)\left(V_{OUT}\right)\left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{\left(L1\right)\left(f\right)}$$

Discontinuous Mode

$$Vp - p = ESR \sqrt{\frac{(2I_{OUT})(V_{OUT})(V_{IN} - V_{OUT})}{L \bullet f \bullet V_{IN}}}$$

Note that only the ESR of the output capacitor is used in the formula. It is assumed that the capacitor is purely resistive at frequencies above 10kHz. If an inductor value has been chosen, the formula can be rearranged to solve for ESR to aid in selecting a capacitor.

Continuous Mode

$$ESR (MAX) = \frac{(Vp - p)(L1)(f)}{V_{OUT} \left(1 - \frac{V_{OUT}}{V_{OUT}}\right)}$$

Discontinuous Mode

$$ESR (MAX) = Vp - p \sqrt{\frac{L \bullet f \bullet V_{IN}}{2I_{OUT} (V_{OUT}) (V_{IN} - V_{OUT})}}$$

Worst case output ripple is at highest input voltage. Ripple is independent of load for continuous mode and proportional to the square root of load current for discontinuous mode.

**Example:** Continuous mode with  $V_{IN(MAX)} = 25V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 3A$ ,  $L1 = 50\mu H$ , f = 100kHz. Required maximum peak-to-peak output ripple is 25mV.

ESR =

$$\frac{(0.025)(50 \times 10^{-6})(10^{5})}{(5)(1 - \frac{5}{25})} = 0.03\Omega$$

(19)

A 10V capacitor with this ESR would have to be several thousand microfarads, and therefore fairly large. Tradeoffs which could be made include:

- A. Paralleling several capacitors if component height is more critical than board area.

- B. Increasing inductance. This can be done at no increase in size if a more expensive core (molypermalloy, etc.) is used.

- C. Adding an output filter. This is often the best solution because the additional components are fairly low cost and their additional space is minimized by being able to "size down" the main L and C. See the "Output Filter" section.

Although ripple current is not usually a problem with buck converter output capacitors because the current is prefiltered by the inductor, a quick check should be done before a final capacitor is chosen—especially if the capacitor has been "downsized" to take advantage of an additional output filter. RMS ripple current into the output capacitor is

Continuous Mode (20)

$$I_{RMS} = \frac{0.29 \left(V_{OUT}\right) \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{L1 \bullet f}$$

From the previous example:

$$I_{RMS} = \frac{0.29 \left(5\right) \left(1 - \frac{5}{25}\right)}{\left(50 \times 10^{-6}\right) \left(10^{5}\right)} = 0.23 \text{A RMS}$$

(21)

This ripple current is low enough to not be a problem, but that could change if the inductor was reduced by two or three to one and the output capacitor was minimized by adding an output filter.

The calculations for discontinuous mode RMS ripple current were considered too complicated for this discussion, but a conservative value would be 1.5 to 2 times output current.

To minimize output ripple, the output terminals of the regulator should be connected directly to the capacitor leads so that the diode (D1) and inductor currents do not circulate in output leads.

#### **Efficiency**

All the losses except those created by the inductor and the output filter are covered in this buck regulator section. The example used was a 5V, 3A output with 25V input. Calculated losses were: switch, 1.24W; diode, 1.2W; switching times, 0.89W; supply current, 0.21W; and input capacitor, 0.17W. Output capacitor losses were negligible. The sum of all these losses is 3.71W. Inductor loss is covered in a special section of this Application Note. Assume for this application that inductor copper loss is 0.3W and core loss is 0.15W. Total regulator loss is 4.16W. Efficiency is

$$E = \frac{I_{OUT} \bullet V_{OUT}}{I_{OUT} \bullet V_{OUT} + \sum P_L} = \frac{(3A)(5V)}{(3A)(5V) + 4.16} = 78\% (22)$$

When considering improvements or tradeoffs of particular loss terms, keep in mind that a change in any one term will be attenuated by efficiency *squared*. For instance, if switch loss were reduced by 0.3W, this is 2% of the 15W output power, but only a  $2(0.8)^2 = 1.28\%$  improvement in efficiency.

#### **Output Divider**

R1 and R2 set DC output voltage. R2 is normally set at  $2.21k\Omega$  (a standard 1% value) to match the LT1074 reference voltage of 2.21V, giving a divider current of 1mA. R1 is then calculated from

$$R1 = \frac{R2 \left(V_{OUT} - V_{REF}\right)}{V_{RFF}}$$

(23)

If R2 = 2.21k

$$\Omega$$

, R1 = (V<sub>OUT</sub> – V<sub>REF</sub>) k $\Omega$

R2 may be scaled in either direction to suit other needs, but an upper limit of  $4k\Omega$  is suggested to ensure that the frequency shifting action created by the FB pin voltage is maintained under shorted output conditions.

#### **Output Overshoot**

Switching regulators often exhibit startup overshoot because the 2-pole LC network requires a fairly low unity gain frequency for the feedback loop. The LT1074 has asymmetrical error amplifier slew rate to help reduce overshoot, but it can still be a problem with certain combinations of L1C1 and C2R3. Overshoot should be checked on all designs by allowing the output to slew from zero in a no-load condition with maximum input voltage. This can be done by stepping the input or by pulling the  $V_{\rm C}$  pin low through a diode connected to a OV-10V square wave.

Worst case overshoot can occur on recovery from an output short because the  $V_C$  pin must slew from its high clamp state down to  $\approx 1.3 V$ . This condition is best checked with the brute force method of shorting and releasing the output.

If excessive output overshoot is found, the procedure for reducing it to a tolerable level is to first try increasing the compensation resistor. The error amplifier output must slew negative rapidly to control overshoot and its slew rate is limited by the compensation capacitor. The compensation resistor, however, allows the amplifier output to "step" downward very rapidly before slewing limitations begin. The size of this step is  $\approx (1.1 \text{mA})(R_C)$ . If  $R_C$  can be increased to  $3k\Omega$ , the  $V_C$  pin can respond very quickly to control output overshoot.

If loop stability cannot be maintained with  $R_C = 3k\Omega$ , there are several other solutions. Increasing the size of the output capacitor will reduce short-circuit-recovery overshoot by limiting output rise time. Reducing current limit will also help for the same reason. Reducing the compensation capacitor below  $0.05\mu F$  helps because the  $V_C$  pin can then slew an appreciable amount during the allowable overshoot time.

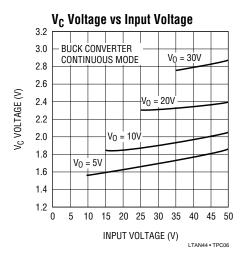

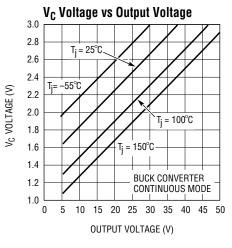

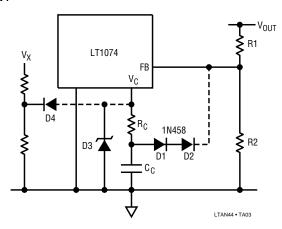

The "final solution" to output overshoot is to clamp the  $V_C$  pin so that it does not have to slew as far to shut off the output. The  $V_C$  pin voltage in normal operation is known fairly precisely because it is made independent of everything except output voltage by the internal multiplier;

$$V_C \text{ Voltage} \approx 2\phi + \frac{V_{OUT}}{24}$$

(24)

$\phi = V_{BE}$  of internal transistor = 0.65V - 2mV/°C

To allow for transient conditions and circuit tolerances, a slightly different expression is used to calculate clamp level for the  $V_{\rm C}$  pin

$$V_{C(CLAMP)} = 2\phi + \frac{V_{OUT}}{20} + \frac{V_{IN(MAX)}}{50} + 0.2V$$

(25)

For a 5V output with  $V_{IN(MAX)} = 30V$ ,

$$V_{C(CLAMP)} = 2(0.65) + \frac{5}{20} + \frac{30}{50} + 0.2 = 2.35V$$

(26)

There are several ways to clamp the  $V_C$  pin as shown in Figure 14. The simplest way is to just add a clamp Zener (D3). The problem is finding a low voltage Zener which does not leak badly below the knee. Maximum Zener leakage over temperature should be  $40\mu A @ V_C = 2\phi + V_{OUT}/20V$ . One solution is to use an LM385-2.5V micropower reference diode where the calculated clamp level does not exceed 2.5V.

Figure 14. Clamping the  $V_{\mbox{\scriptsize C}}$  Pin

A second clamp scheme is to use a voltage divider and diode (D4).  $V_X$  must be some quasi-regulated source which does not collapse with regulator output voltage. A third technique can be used for outputs up to 20V. It clamps the  $V_C$  pin to the feedback pin with two diodes, D1 and D2. These are small signal nongold doped-diodes with a forward voltage that matches  $\phi$ . The reason for this is start-up.  $V_C$  is essentially clamped to ground through the output divider when  $V_{OUT} = 0$ . It must be allowed to rise

sufficiently to ensure start-up. The feedback pin will sit at about 0.5V with  $V_{OUT}=0$ , because of the combined current from the feedback pin and  $V_C$  pin. The  $V_C$  voltage will be  $2\phi+0.5V+(0.14mA)$  (R<sub>C</sub>). With R<sub>C</sub> =  $1k\Omega$ ,  $V_C=1.94$ . This is plenty to ensure start-up.

#### **Overshoot Fixes that Don't Work**

I know that these things don't work because I tried them. The first is soft start, created by allowing the output current or the  $V_{\mathbb{C}}$  voltage to ramp up slowly. The first problem is that a slowly rising output allows more time for the  $V_{\mathbb{C}}$  pin to ramp up well beyond its nominal control point so that it has to slew farther down to stop overshoot. If the  $V_{\mathbb{C}}$  pin itself is ramped slowly, this can control input start-up overshoot, but it becomes very difficult to guarantee reset of the soft start for all conditions of input sequencing. In any case, these techniques do not address the problem of overshoot following overload of the output, because they do not get "reset" by the output.

Another common practice is to parallel the upper resistor in the output divider with a capacitor. This again works fine under limited conditions, but it is easily defeated by overload conditions which pull the output slightly below its regulated point long enough for the  $V_{C}$  pin to hit the positive limit ( $\approx$ 6V). The added capacitor remains charged and the  $V_{C}$  pin must slew almost 5V to control overshoot when the overload is released. The resulting overshoot is impressive—and often deadly.

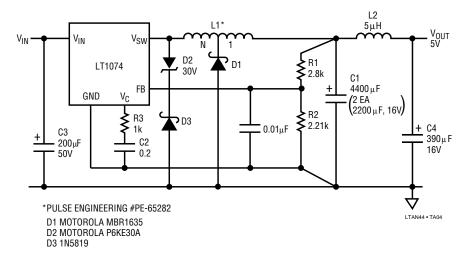

#### TAPPED-INDUCTOR BUCK CONVERTER

Output current of a buck converter is normally limited to maximum switch current, but this restriction can be altered by tapping the inductor as shown in Figure 15. The ratio of "input" turns to "output" turns is "N" as shown in the schematic. The effect of the tap is to lengthen switch "on" time and therefore draw more power from the input without raising switch current. During switch "on" time, current delivered to the output through L1 is equal to switch current—5.5A maximum for the LT1074. When the switch turns off, inductor current flows only in the output section of L1, labeled "1," through D1 to the output. Energy conservation in the inductor requires that current increase by the ratio (N+1):1. If N=3, then maximum current delivered to the output during switch

Figure 15. Tapped-Inductor Buck Converter

off time is (3 + 1)(5.5A) = 22A. Average load current is increased to the weighted average of the 5A and 22A currents. Maximum output current is given by;

$$0.95 \left[ I_{SW} - \frac{\left( V_{IN'} - V_{OUT'} \right) \left( 1 + N \right)}{2 Lf \left( N + \frac{V_{IN'}}{V_{OUT'}} \right)} \right] \left[ \frac{N+1}{1 + \frac{N \bullet V_{OUT'}}{V_{IN'}}} \right]$$

L = Total Inductance

The last term,  $(N+1)/(1+N\bullet V_{OUT}/V_{IN})$  is the basic switch current multiplier term. At high input voltages it approaches N+1, and theoretical output current approaches 18A for N=3. For lower input voltages the multiplier term approaches unity and no benefit is gained by tapping the inductor. Therefore, when calculating maximum load current capability, always use the worst case low input voltage. The 0.95 multiplier is thrown-in to account for second order effects of leakage inductance, etc.

**Example:**  $V_{IN(MIN)} = 20V$ , N = 3,  $L = 100 \mu H$ ,  $V_{OUT} = 5V$ , Diode  $V_f = 0.55V$ , f = 100 kHz. Let  $I_{SW} = Maximum$  for LT1074 = 5.5A,  $V_{OUT}' = 5V + 0.55V = 5.55V$ ,  $V_{IN}' = 20V - 2V = 18V$

Duty cycle of the tapped-inductor converter is equal to;

$$DC = \frac{1 + N}{N + \frac{V_{1N'}}{V_{0UT'}}}$$

(29)

Average and peak diode currents are

$$I_{D(AVG)} = \frac{I_{OUT} \left( V_{IN'} - V_{OUT'} \right)}{V_{IN'}}$$

(30)

$$\left( \text{Use Maximum } V_{IN'} \right)$$

$$\begin{split} I_{D(PEAK)} &= \frac{I_{OUT} \left(N \ V_{OUT}' + V_{IN'}\right)}{V_{IN'}} \\ &\left(Use \ Minimum \ V_{IN'}\right) \end{split}$$

Average switch current during switch on time is

$$I_{SW(AVG)} = \frac{I_{OUT} \left( N \bullet V_{OUT}' + V_{IN}' \right)}{V_{IN}' \left( 1 + N \right)}$$

(31)

(Use Minimum  $V_{IN}'$ )

,

Diode peak reverse voltage is

$$V_{DI(PEAK)} = \frac{V_{IN} + N \bullet V_{OUT}}{1 + N}$$

(32)

(Use Maximum  $V_{IN}$ )

Switch reverse voltage is

$$V_{SW} = V_{IN} + V_Z + V_{SPIKE}$$

(Use Maximum  $V_{IN}$ ) (33)

$V_Z$  = Reverse breakdown of D2 (30V)

$V_{SPIKE}$  = Narrow (<100ns) spike created by rapid switch turnoff and the stray wiring inductance of C3, D2, D3, and the LT1074  $V_{IN}$  and switch pins. This voltage spike is approximately  $I_{SW}/2$  *volts per inch* of total lead length.

Using parameters from the maximum output current example, with  $V_{IN(MAX)} = 30V$ ,  $I_{OUT} = 8A$

DC @

$$V_{IN} = 20V = \frac{1+3}{3+\frac{18}{5.55}} = 64\%$$

(34)

$I_{D(AVG)} = \frac{(8)(28-5.55)}{28} = 6.7A$

$I_{D(PEAK)}$  @  $V_{IN} = 20V = \frac{(8)(3 \cdot 5.55 + 18)}{18} = 15.4A$

$I_{SW(AVG)}$  @  $V_{IN} = 20V = \frac{(8)(3 \cdot 5.55 + 18)}{18(1+3)} = 3.85A$

Note that this is the average switch current during "on" time. It must be multiplied by duty cycle and switch voltage drop to obtain switch power loss. Total loss also includes switch fall time (rise time losses are minimal due to leakage inductance in L1).

$$\begin{split} P_{SWITCH} &= \left(I_{SW}\right) \left(DC\right) \left[1.8V + \left(0.1\right) \left(I_{SW}\right)\right] + \\ & \left(V_{IN}' + V_Z\right) \left(I_{SW}\right) \left(f\right) \left(t_{SW}\right) \\ t_{SW} &= 50 \text{ns} + 3 \text{ns} \bullet I_{SW} \\ &= \left(3.85\right) \left(0.64\right) \left[1.8 + \left(0.1\right) \left(3.85\right)\right] + \\ & \left(20 + 30\right) \left(3.85\right) \left(10^5\right) \left(62 \text{ns}\right) \\ &= 5.3W + 1.19W = 6.5W \end{split}$$

$$V_{DI\left(PEAK\right)} &= \frac{30 + 3.5}{1 + 3} = 11.25V \tag{36}$$

$$V_{SW} &= 30 + 30 + \frac{3.85}{2} \left(2''\right)^* = 64V \end{split}$$

\* This assumes 2" of lead length

#### Snubber

The tapped-inductor converter requires a snubber (D2 and D3) to clip off negative switching spikes created by the leakage inductance of L1. This inductance  $(L_1)$  is the value measured between the tap and the switch (N) terminal with the tap shorted to the output terminal. Theoretically. the measured inductance will be zero because the shorted turns reflect "0" ohms back to any other terminals. In practice, even with bifilar winding techniques, there is ≥1% leakage inductance compared to total inductance. This is  $\approx 1.2 \mu H$  for the PE-65282. L<sub>I</sub> is modeled as a separate inductance in series with the "N" section input, which does not couple to the rest of the inductor. This gives rise to a negative spike at the switch pin at switch turnoff. D2 and D3 clip this spike to prevent switch damage, but D2 dissipates a significant amount of power. This power is equal to the energy stored in  $L_1$  at switch turnoff,  $(E = (I_{SW})^2 \bullet L_L/2)$  multiplied by switching frequency and a multiplier term which is dependent on the difference between D2 voltage and the normal reverse voltage swing at the inductor input.

$$P_{D2} = \frac{\left(I_{SW}\right)^2 \bullet L_L}{2} \left(f\right) \left(\frac{V_Z}{V_Z - V_{OUT}' \bullet N}\right) \tag{37}$$

For this example;

$$P_{D2} = (38)$$

$$\frac{(3.85)^{2} (1.2 \times 10^{-6}) (10^{5})}{2} (\frac{30}{30 - 5.55 \cdot 3}) = 2W$$

### **Output Ripple Voltage**

Output ripple on a tapped-inductor converter is higher than a simple buck converter because a square wave of current is superimposed on the normal triangular current fed to the output. Peak-to-peak ripple current delivered to the output is:

$$\begin{split} & Ip - p = & (39) \\ & \frac{I_{OUT} \left( N \bullet V_{OUT} + V_{IN} \right) \left( N \right)}{V_{IN} \left( 1 + N \right)} + \frac{\left( 1 + N \right) \left( V_{IN} - V_{OUT} \right)}{f \bullet L \left( N + \frac{V_{IN}}{V_{OUT}} \right)} \\ & \left( Use \, Minimum \, \, V_{IN} \right) \end{split}$$

A conservative approximation of RMS ripple current is one-half of peak-to-peak current.

Output ripple voltage is simply the ESR of the output capacitor multiplied times lp-p. In this example, with ESR =  $0.03\Omega$

$$\frac{(8)(3 \cdot 5 + 20)(3)}{20(1+3)} + \frac{(1+3)(20-5)}{(10^5)(10^{-4})(3+\frac{20}{5})} = 11.4A$$

$$I_{RMS} = 5.7A$$

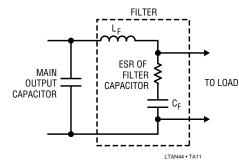

$Vp - p = (0.03)(11.4) = 340mV$

This high value of ripple current and voltage requires some thought about the output capacitor. To avoid an excessively large capacitor, several smaller units are paralleled to achieve a combined 5.7A ripple current rating. The ripple voltage is still a problem for many applications. However, to reduce ripple voltage to 50mV would require an ESR of less than 0.005W—an impractical value. Instead, an output filter is added which attenuates ripple by more than 20:1.

#### **Input Capacitor**

The input bypass capacitor is selected by ripple current rating. It is assumed that all the converter input ripple current is supplied by the input capacitor. RMS input ripple current is approximately

$$\begin{split} I_{IN\left(RMS\right)} &\approx \frac{\left(I_{OUT}\right)\left(V_{OUT}\right)}{\left(V_{IN}\right)\left(1+N\right)} \, \sqrt{\left(1+N\right)\left(\frac{V_{IN}}{V_{OUT}}-1\right)} \quad \text{(41)} \\ &\left(Use\,Minimum\ V_{IN}\right) \end{split}$$

$$= \frac{(8)(5.5)}{(18)(1+3)} \sqrt{(1+3)\left(\frac{18}{5.5}-1\right)} = 1.84A \text{ RMS}$$

The input capacitor value in microfarads is not particularly important since it is purely resistive at 100kHz; but it must be rated at the required ripple current and maximum input voltage. Radial lead types should be used to minimize lead inductance.

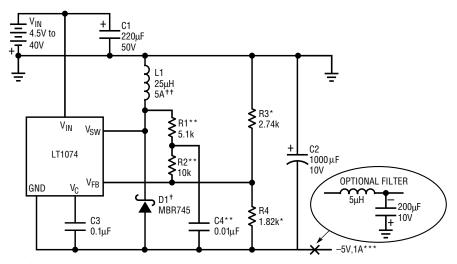

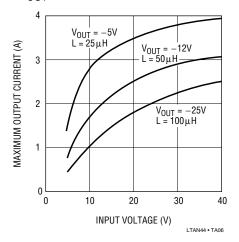

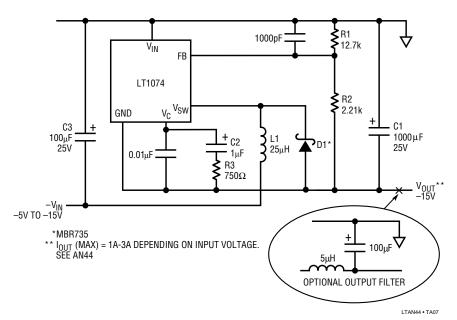

#### POSITIVE TO NEGATIVE CONVERTER

The LT1074 can be used to convert positive voltages to negative if the *sum* of input and output voltage is greater than the 8V minimum supply voltage specification, and the minimum positive supply is 4.75V. Figure 16 shows the LT1074 used to generate negative 5V. The ground pin of the device is connected to the negative output. This allows the feedback divider, R3 and R4, to be connected in the normal fashion. If the ground pin were tied to ground, some sort of level shift and inversion would be required to generate the proper feedback signal.